이 포스팅은 제 개인적인 공부를 저장 및 복습하기 위해서 올리는 글입니다. 개인적인 정리기 때문에 저의 잘못된 이해가 섞여있을수도 있는 점 알려드립니다. 너무 맹신하지는 말아 주시기 바랍니다.

게이트 기본 요소 (primitive)

게이트 기본 요소 (gate primitive)는 버퍼 (buffer)와 인버터 (invertor)를 제외하고 여러 입력과 한 개의 출력을 갖는다. 그에 반하여 버퍼와 인버터는 여러 개의 출력과 한 개의 입력을 갖는다. 인수의 순서는 출력이 먼저 나오고 그 다음 입력이 나온다.

게이트 | 설명 | 사용 예 |

or | N입력 OR | or(out, in1, in2, ..., inN) |

nor | N입력 NOR | nor(out, in1, in2, ..., inN) |

and | N입력 AND | and(out, in1, in2, ..., inN) |

nand | N입력 NAND | nand(out, in1, in2, ..., inN) |

xor | N입력 XOR | xor(out, in1, in2, ..., inN) |

xnor | N입력 XNOR | xnor(out, in1, in2, ..., inN) |

예를 들어서 위의 게이트 기본 요소를 부품으로 가져오는 요령은 다음과 같이 하면 된다.

and #(12, 9) [3:0] u3 (y, a, b, c)

이것이 의미는 3 입력 a, b, 및 c를 받아 출력 y를 출력하는 3입력 and 게이트 기본 요소의 부품 이름에 u3라고 명명했으며 이런 3입력 and가 나란히 4개가 있다는 뜻이다.

AND, OR, 및 NOR의 진리표를 다음 그림에서 보였다.

XOR | 0 | z | x | z |

0 | 0 | 1 | x | x |

1 | 1 | 0 | x | x |

x | x | x | x | x |

z | x | x | x | x |

AND | 0 | 1 | x | z |

0 | 0 | 0 | 0 | 0 |

1 | 0 | 1 | x | x |

x | 0 | x | x | x |

z | 0 | x | x | x |

XOR | 0 | z | x | z |

0 | 0 | 1 | x | x |

1 | 1 | 0 | x | x |

x | x | x | x | x |

z | x | x | x | x |

AND | 0 | 1 | x | z |

0 | 0 | 0 | 0 | 0 |

1 | 0 | 1 | x | x |

x | 0 | x | x | x |

z | 0 | x | x | x |

OR | 0 | 1 | x | z |

0 | 0 | 1 | x | x |

1 | 1 | 1 | 1 | 1 |

x | x | 1 | x | x |

z | x | 1 | x | x |

전송 게이트 (Transmission Gate)

전송 게이트 기본 요소 (transmission gate primitive)는 다음과 같다.

게이트 | 설명 | |

buf | N출력 버퍼 | buf(out1, out2, ..., outN, in) |

not | N출력 인버터 | not(out1, out2, ..., outN, in) |

bufif1 | N출력 3상태 버퍼, 활성 높은 en | bufif1(out1, out2, ..., outN, in, control) |

notif1 | N출력 3상태 인버터, 활성 높은 en | notif1(out1, out2, ..., outN, in, control) |

bufif0 | N출력 3상태 버퍼, 활성 낮은 en | bufif0(out1, out2, ..., outN, in, control) |

notif0 | N출력 3상태 인버터, 활성 낮은 en | notif0(out1, out2, ..., outN, in, control) |

buf |

|

0 | 0 |

1 | 1 |

x | x |

z | x |

inv |

|

0 | 1 |

1 | 0 |

x | x |

z | x |

buf와 inv에 대한 진리표

buf |

|

0 | 0 |

1 | 1 |

x | x |

z | x |

inv |

|

0 | 1 |

1 | 0 |

x | x |

z | x |

buf와 inv에 대한 진리표

스위치 (Switch) 기본 요소 (Primitive)

스위치 기본 요소 (switch primitive)로는 다음과 같다.

게이트 | 설명 | 사용 예 |

pmos | 단방향 PMOS 스위치 | pmos(out, data, control) |

rpmos(r이 붙이니 저항갖는듯) | 저항을 가진 단방향 PMOS 스위치 | rpmos(out, data, control) |

nmos | 단방향 NMOS 스위치 | nmos(out, data, control) |

rnmos | 저항을 가진 단방향 NMOS 스위치 | rnmos(out, data, control) |

cmos | 단방향 CMOS 스위치 | cmos(out, data, ncontrol, pcontrol) |

rcmos | 저항을 가진 단방향 CMOS 스위치 | rcmos(out, data, control) |

tranif1 | 양방향 트랜지스터 (활성 높은 제어) | tranif1(inout1, inout2, control) |

tranif0 | 양방향 트랜스지스터(활성 낮은 제어) | tranif0(inout1, inout2, control) |

게이트 | 설명 | 사용 예 |

rtranif1 | 저항을 가진 양방향 트랜지스터(활성 높은 제어) | rtranif1(inout1, inout2, control) |

rtranif0 | 저항을 가진 양방향 트랜지스터(활성 낮은 제어) | rtranif0(inout1, inout2, control) |

tran | 양방향 통과 트랜지스터 | tran(inout1, inout2) |

rtran | 저항을 가진 양방향 통과 트랜지스터 | rtran(inout1, inout2) |

pullup | 풀업 저항 |

|

pulldown | 풀다운 저항 |

|

if가 붙으면 3상이 돼서 control 포트가 생김, 1이 붙으면 고활성 0이 붙으면 저활성

저항을 가진 장치들은 신호의 세기 (strength)를 한 단계 약화 시키는 목적으로 사용된다.

신호 세기 (strength) 수준

신호 세기 (signal strength)는 다음과 같이 8단계가 있다. 높은 번호가 더 세다.

신호 수준 | 사용 예 |

7 | supply0, supply1 |

6 | strong0, strong1 |

5 | pull0, pull1 |

4 | large |

3 | weak0, weak1 |

2 | medium |

1 | small |

0 | highz0, highz1 |

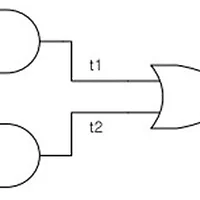

그림 5.6 두 개의 드라이버를 갖는 연결

만약 A 신호의 세기가 pull1이고 B의 신호 세기가 supply0 라면 C의 신호의 세기는 B의 값을 취한다.

게이트와 스위치 지연

실제 회로에서 논리 게이트들은 전달 지연 (propagation delay)을 갖게 된다. verilog는 각 게이트에 이러한 지연을 주는 구조를 갖고 있다. 지연에는 상승 시간 (rising time), 하강 시간 (falling time), 꺼지는 시간 (turn-off time)을 가질 수 있다. 또한 각 시간 별로 최대값 (maximum value), 전형적인 값 (typical value), 및 최소값 (minimum vaule)들을 줄 수 있다. 상승 시간은 0, x, 및 z에서 1로 천이되는데 걸리는 시간이고, 하강 시간은 1, x, 및 z에서 0으로 천이하는데 걸리는 시간이며 꺼지는 시간은 0, 1, 및 x에서 z로 천이하는데 걸리는 시간이다. (z는 고임피던스, 전압(신호)를 먹는 역활을 고임피던스가 한다.)

조건 | 온도 | 전압 | 회로 |

Typical | 실온 | 보통 전압 |

|

maximum | 고온 | 낮은 전압 | 느린 회로 |

Minimum | 저온 | 높은 전압 | 빠른 회로 |

게이트에 대한 전달 지연에 대한 예로 들어 and #(8) n1 (q, a, b)는 다음 두 가지를 의미한다.

a와 b를 입력으로 하는 and게이트가 8 시간 후에 q 출력된다.

입력으로 들어온 8보다 더 작은 펄스폭은 출력에 영향을 주지 않는다.

이런 지연을 관성 지연 (inertial delay)이라고 한다. 펄스 폭에 상관없이 출력에 영향을 미치는 지연을 전송 지연(transport delay)이라고 한다.

이에 반하여 넷 지연(net delay)는 다음과 같이 사용하면 된다.

wire #<delay_time> <variable>

즉 변수까지 넷을 통하여 값이 전달되는데 지연 시간 만큼 지연된다. 값이 하나일때는 그 값이 세가지 지연 모두에게 적용된다. 두 개가 있을 때는 상승 시간과 하강 시간에 두값을 적용하고 x나 z로의 천이 시간은 두 값 중의 작은 값이 적용된다. 없는 지연 값은 주어진 값들 중 최소값을 이용함을 알 수 있다. 즉 wire #5 a는 a까지 전달되는데 걸리는 지연 시간이 5 시간 소요된다.

'Study > Verilog' 카테고리의 다른 글

| Verilog : UDP (user-defined primitve) (0) | 2017.05.05 |

|---|---|

| Verilog : 연산자 (3) | 2017.04.28 |

| Verilog : 모듈가져오기 (0) | 2017.04.28 |

| Veriliog : 상수 선언, 모듈, 포트 (1) | 2017.04.28 |

| Verilog의 기본 : 숫자표현, 자료형, 벡터, 배열, 문자열 (0) | 2017.04.28 |