이 포스팅은 제 개인적인 공부를 저장 및 복습하기 위해서 올리는 글입니다. 개인적인 정리기 때문에 저의 잘못된 이해가 섞여있을수도 있는 점 알려드립니다. 너무 맹신하지는 말아 주시기 바랍니다.

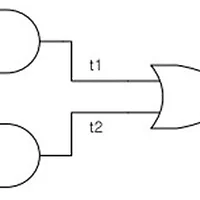

UDP 란 내가 만들고 싶은 게이트를 만들어내는 것!

UDP 포트의 규칙

UDP 포트 출력신호는 단 하나이고 입력은 최대 10개까지 만들 수 있다. 첫 번째 신호가 항상 출력이고 그 다음의 나머지 신호들의 입력이다. 스칼라 신호만 허용되고 벡터 신호는 허용되지 않는다. UDP는 양방향(inout) 신호를 허용하지 않는다. 순차적 UDP는 출력 포트에 대한 reg 자료형 선언을 추가로 해야한다.

UDP에서 사용하는 특수 기호

상승 예지, don’t-care 조건 등 특수한 기호를 사용 할 수 없다.

기호 | 해석 | 주석 |

0 | 0 상태 |

|

1 | 1 상태 |

|

x | 모르는 상태 |

|

? | 0, 1, x의 반복 | 출력 필드에서는 사용 불가(출력은 결과값인데 애매한 값이 나오면 안되지) |

b | 0,1의 반복(b는 2진수니까) | 출력 필드에서는 사용 불가(마찬가지) |

- | 변화 없음 | 출력 필드에서만 사용 가능(입력에 따른 출력의 변화를 나타는 기호이다) |

(vw) | v에서 w로 값 변화 | v와 w는 0, 1, x, ?, 혹은 b를 가질 수 있다. (이것도 출력에선 못쓰지 않을까) |

* | (??) | 어떠한 값 변화 |

r | (01) | 상승 예지 |

f | (10) | 하강 예지 |

p | (01), (0x), 그리고 (x1) | 양수 예지 |

n | (10), (1x), 그리고 (x0) | 음수 예지 |

UDP 몸체(UDP body)는 table-endtalbe로 묶는다. 순차적 UDP의 경우 initial을 이용하여 출력에 초기값을 줄 수 있다. UDP 몸체의 예를 다음이 보였다. 간단하게 a = b | c를 구현해본다. UDP에서는 z를 입력으로 사용하지 않는 것에 주의하라. 여기서 ?는 0, 1, 및 x 중 무엇이 와도 된다는 무정의 (don’t-care, 뭔지 모름) 조건을 의미한다. 각 줄마다 입력과 출력으로 분리된다. UDP 몸체에 있는 입력 신호의 순서는 UDP 포트 신호에서 선언된 순서와 일치해야 한다. 입력과 출력은 콜론 (;)으로 구분해야 한다. 각 행은 세미콜론 (;)으로 끝내야한다. 새로운 입력이 들어오면 table 내에 있는 각 행의 입력과 비교하여 해당되는 행의 출력을 낸다. 일치하는 행이 없으면 x출력을 낸다.

primitive udp_or_gate(a,b,c);

output a;

input b, c;

//UDP_body a = b | c

table

// b c : a

? 1 : 1;

1 ? : 1;

0 0 : 0;

endtable

endprimitive

다음은 initial을 이용하여 초기값을 준 예이다.

primitive udp_or_initial(a, b, c);

output a;

input b, c;

initial begin

a=1’b1;

end

table

// a=b|c

//b c: a

? 1: 1;

1 ?: 1;

0 0: 0;

endtable

endprimitive

같은 입력 조합에 다른 출력값을 주면 잘못된 것이다.

'Study > Verilog' 카테고리의 다른 글

| Verilog : 게이트 (0) | 2017.04.28 |

|---|---|

| Verilog : 연산자 (3) | 2017.04.28 |

| Verilog : 모듈가져오기 (0) | 2017.04.28 |

| Veriliog : 상수 선언, 모듈, 포트 (1) | 2017.04.28 |

| Verilog의 기본 : 숫자표현, 자료형, 벡터, 배열, 문자열 (0) | 2017.04.28 |